2017年5月2日

特约作者:迪克·詹姆斯,名誉研究员

在此期间伊卡卡特会议去年2月,索尼发布了一份新闻稿“行业的第一个3层堆叠CMOS图像传感器,具有DRAM for Smartphones”.几年来一直有关于图像传感器嵌入DRAM(加速图像数据处理)的传言,但到目前为止,还没有投入生产并在现实世界中使用。

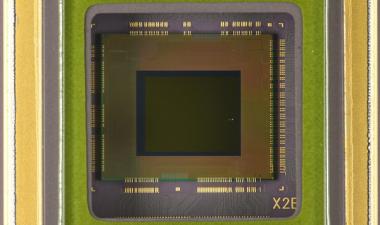

详细信息在亚卡卡会议上的论文[1]中给出了,它实际上看起来像真实的东西,所以这绝对引起了我们在TechInsights内的图像传感器专家的注意。在移动世界大会上确认其生产状况,索尼发布了他们的Experia XZ Premium和XZ手机,带有960 fps的运动眼镜摄像头系统。我们一旦有空,我们就掌握了Xperia XZS,横断面的镜面相机芯片和Lo和Phoold,我们确实有一个三堆叠;CMOS图像传感器(CIS)在DRAM上靠背安装,与图像信号处理器(ISP)面对面。

下载我们的分析产品摘要

本产品简介总结了我们打算建立的可交付成果以及对部件的技术相关性的一些额外评论。

然而,我们有点超前了,所以让我们看看索尼的新闻稿和ISSCC的论文。

在早期的1900万像素图像传感器中,索尼使用了双数字/模拟转换器来数字化像素数据,现在我们有了一个4层结构,以提高读数速度,并提高处理能力。DRAM用于临时存储高速数据,然后以最优速率输出给传感器接口。这种设计使得它可以在1/120秒内读取1930万像素的静态图像,在电影模式下,它可以高达1000 fps,比早期产品分别快4倍和8倍。这个框图说明了信号路径。

鉴于DRAM夹在CIS和ISP之间,高速数据必须通过内存芯片到ISP,然后在其通过I / F(接口)块之后ISP,以常规速度适用于应用处理器。

这是一个压缩版的传感器操作;论文详细介绍了960帧每秒成像和慢动作的工作原理。索尼的示意图说明了这三层结构。

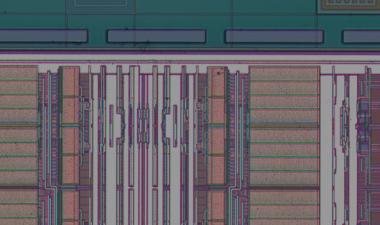

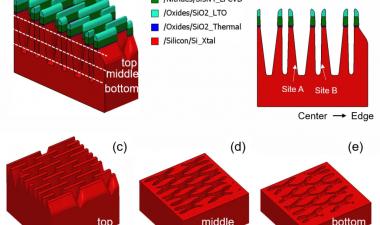

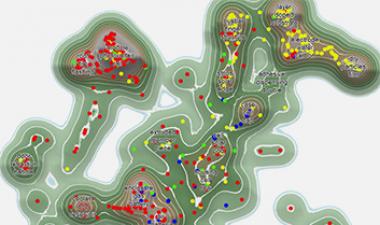

根据本文,像素阵列位于上模,DRAM阵列和行驱动位于中间模,其余块位于底部ISP模。我们还没有所有三个骰子的照片,但这张纸上有一些图像。

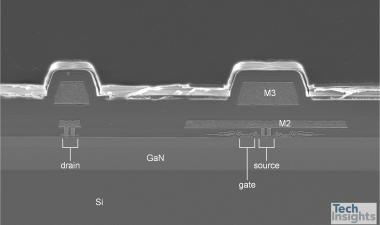

索尼还告诉我们,CIS在90nm,1 al,5铜技术中制作,DRAM为1 GB,30nm(3 Al,1 W)部分,ISP为40nm,1 al,6 CU设备。无疑是让所有功能所需的所有功能都有三个相同尺寸的挑战,而不会浪费硅区域。

鉴于DRAM DIA也有CIS行驱动程序,那么它必须设计为自定义部分,而不是我们最近看到的TSV启用(TSV =通过硅通孔)商品DRAM之一年。索尼的横截面还表明,中心模具具有厚的氧化物和降落垫,用于从上方的顺式下降。

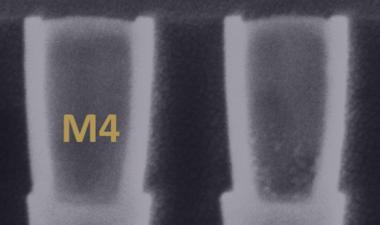

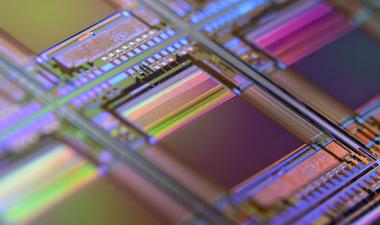

We can also see (if the scale bar is accurate), that the CIS and DRAM die substrates have been thinned down to ~2.6 µm, normal for a back-illuminated CIS (BI-CIS), but that’s the thinnest DRAM we have ever seen. Our own image (above) confirms that the CIS and DRAM silicon are of the same order in thickness, and the landing pads are also visible.

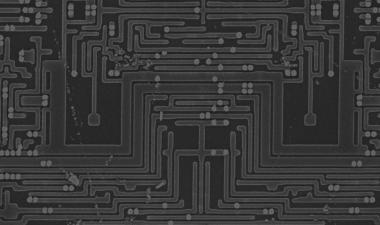

下一个问题是 - TSV在堆栈中如何形成?我们的第一个横截面刚刚走出实验室,他们看起来很熟悉。CIS / DRAM连接似乎是我们在早期几代索尼背光(BI)CIS设备中看到的TSV的上环绕形式。

这里有两层TSV,将CIS中的一个6金属叠层连接到DRAM模具的M1。我们没有扩展TSV的横截面将CIS直接加入ISP,尽管有TSV通过DRAM到ISP的顶部金属。

CIS / ISP连接似乎可以使用DRAM着陆垫层作为互连,以避免在形成完整堆叠之后钻孔钻孔的挑战。

对IMX400的进一步分析正在进行中,在适当的时候,我们将有关于CIS本身和包堆栈的报告。从行业角度来看,索尼再次突破了手机相机的极限。今年晚些时候最大的问题是——我们会在下一代iPhone上看到这一点吗?

参考:

[1] T. Haruta等,“A 1 / 2.3英寸20mpixel 3层堆叠CMOS图像©2017 IEEE传感器与DRAM”,Proc。ISSCC 2017,Paper 4.6