4部分博客系列:智能手机成像仪的艺术状态

第3部分:背照有源硅厚度,深沟隔离(DTI)

发布日期:2019年7月23日

撰稿人:雷·方丹

内容改编自TechInsights为2019年国际图像传感器研讨会(IISW)撰写的论文

此次演讲的博客提纲分为四个部分:

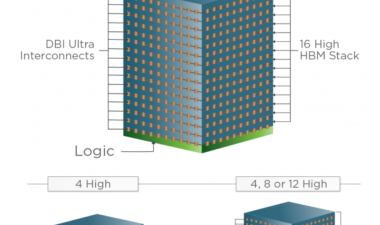

(1)芯片堆叠和芯片到芯片互连那

(2)像素缩放和缩放使能器那

(3)有源硅厚度与深沟隔离(DTI)结构,和

(4)非拜耳滤色器阵列和相位检测自动对焦(PDAF)。

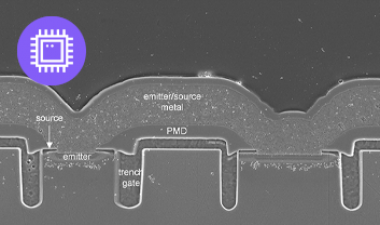

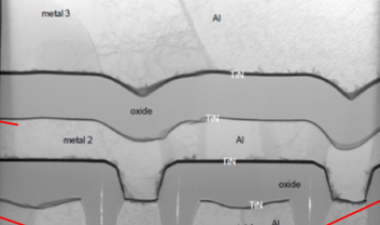

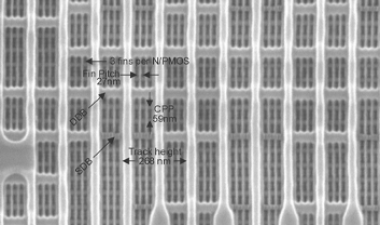

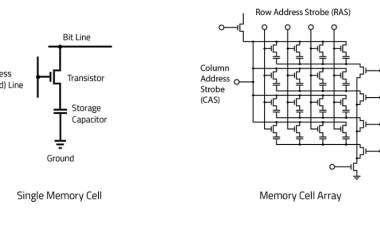

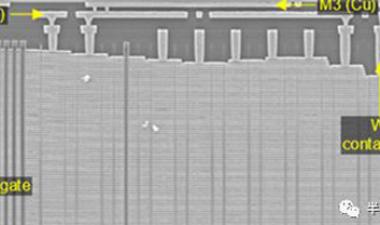

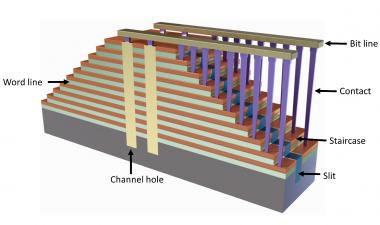

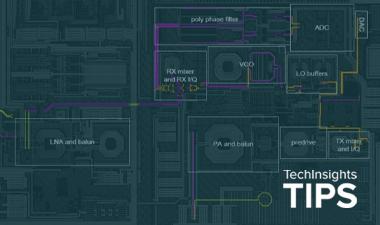

在本博客系列的第2部分中,我们将DTI确定为关键的小像素缩放启用程序,但为什么呢?为什么DTI对小像素性能如此重要?

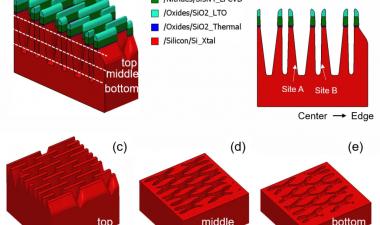

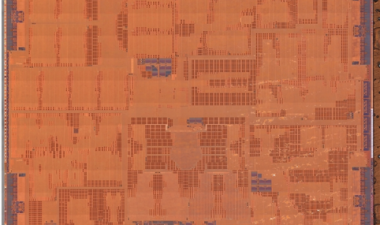

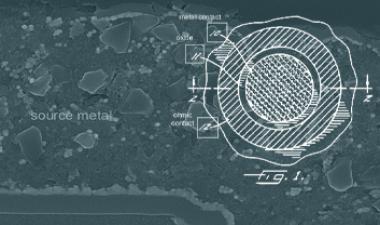

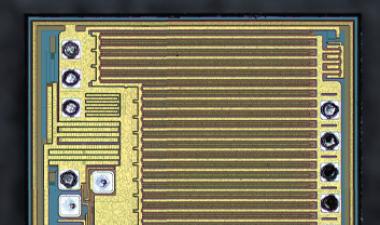

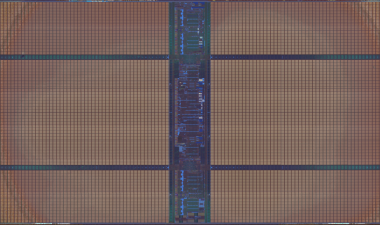

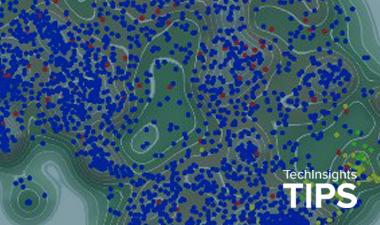

图1示出了缩放后照明像素中的主要挑战,其包括保持可接受的光电二极管全阱容量(FWC)并抑制串扰。FWC问题通过增加有源Si厚度来溶解;然而,在没有高性能的DTI结构的情况下,串扰问题将是一个限制因素。

从概念上讲,DTI结构很容易理解。这些可以在前面的处理流的早期(前DTI,或F-DTI)实现,或者在活动Si细化处理(后DTI,或B-DTI)之后的更晚的处理流中实现。这两种策略都是在大批量生产的今天,都需要谨慎的发展,以减轻暗电流问题所产生的DTI蚀刻过程。

图1:小像素缩放,DTI结构

智能手机成像仪的最先进

从TechInsights在IISW 2019的演讲中下载我们的论文和幻灯片。

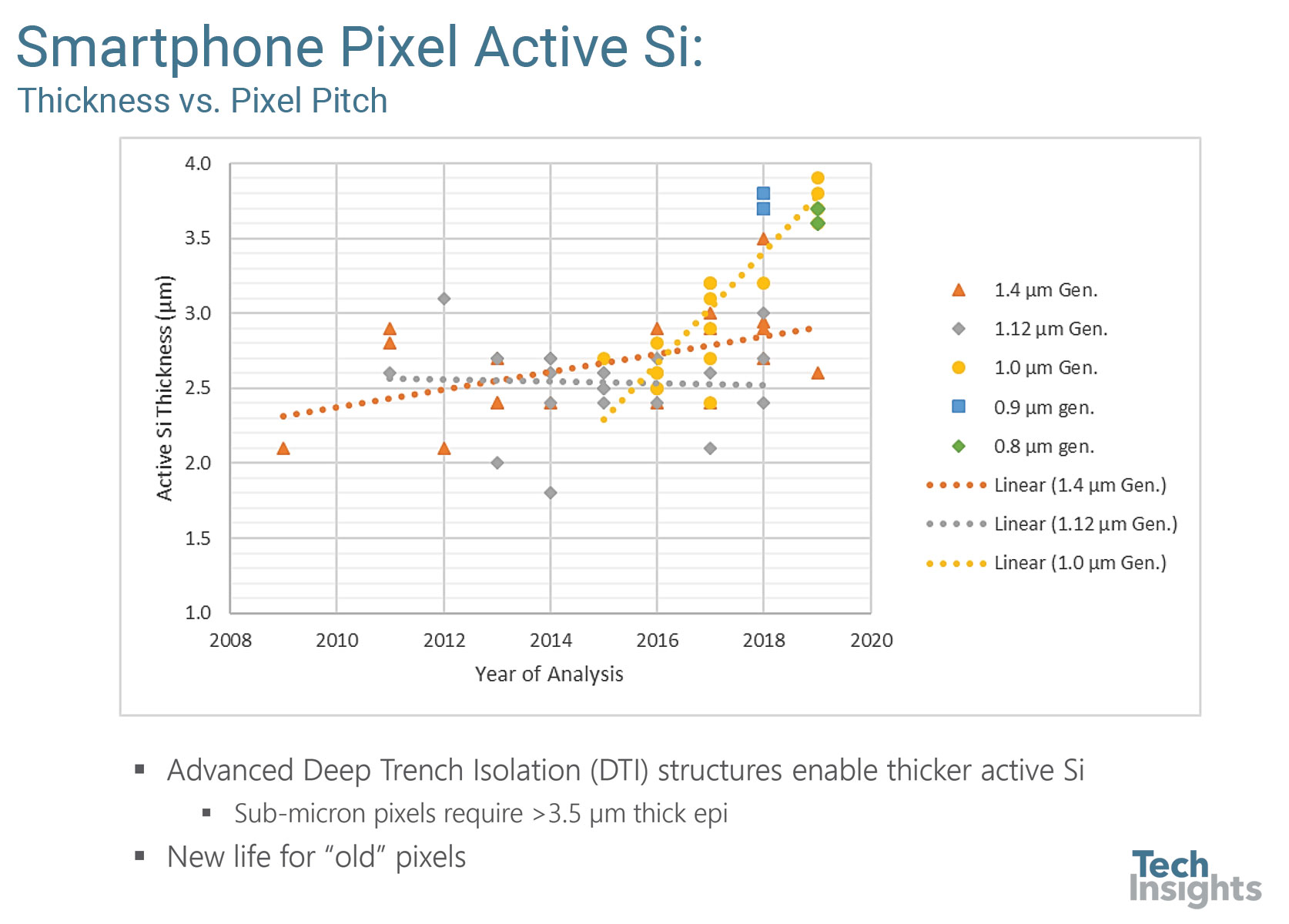

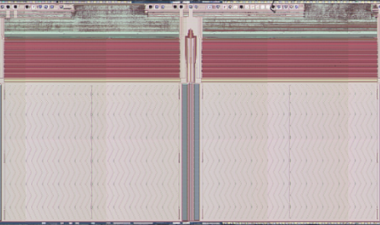

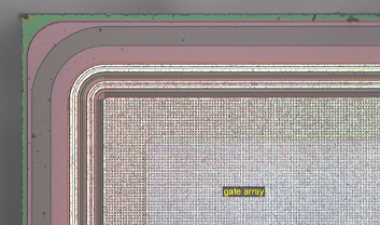

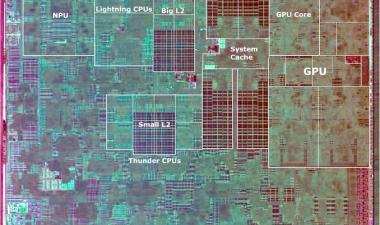

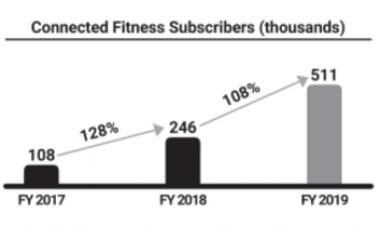

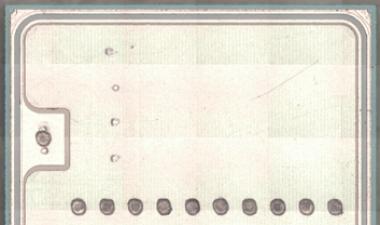

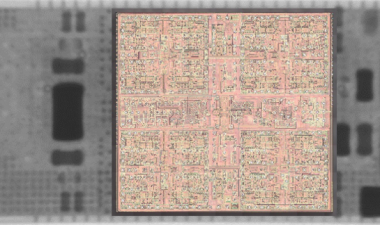

图2显示了按像素生成的选定旗舰智能手机成像仪像素的活动硅厚度调查。我们的逆向工程内容仔细地记录了IDM/foundry的F-DTI/B-DTI演进,但是为了这个博客的目的,数据集已经被简化以显示高级趋势。乐动篮球快讯

DTI首先被引入到具有传统的或稍厚的有源Si的背光像素中,然后被优化以使随着时间的推移有源Si显著地厚。例如,DTI早期达到1.0µm像素,具有2.5µm到2.7µm的有源Si厚度,后来启用了高达3.9µm的有源Si厚度。研究0.8µm和0.9µm像素代可以清楚地看出,选择>3.5µm的有源Si厚度以实现足够的像素性能。我们记录的另一个策略是在较旧的像素设计中部署这些较新的DTI结构。事实上,苹果最近的iPhone成像仪不仅扭转了iPhone像素从1.22µm到1.4µm的缩放趋势,而且同时增加了由B-DTI结构实现的有源Si厚度。

图2:背光有源硅厚度趋势

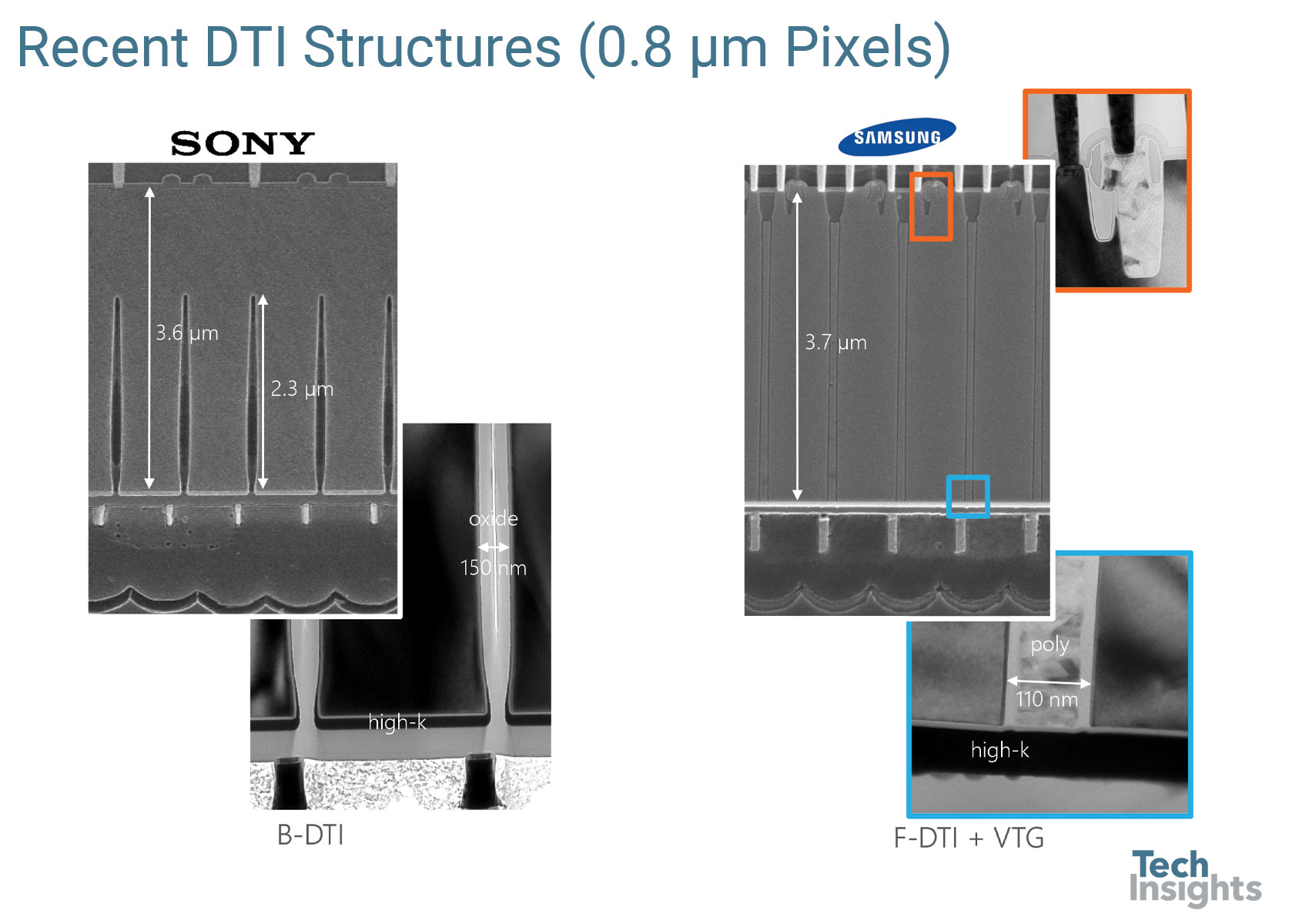

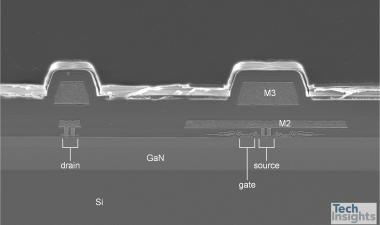

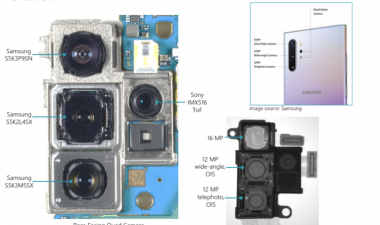

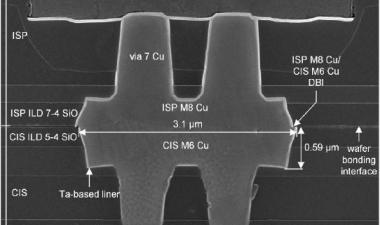

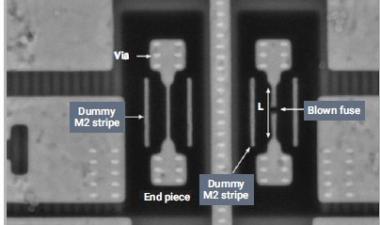

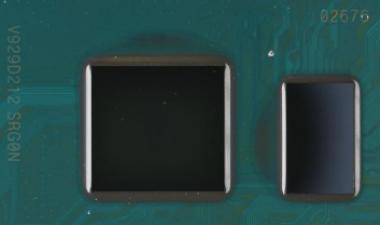

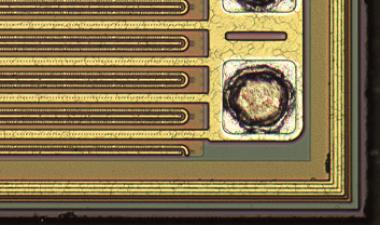

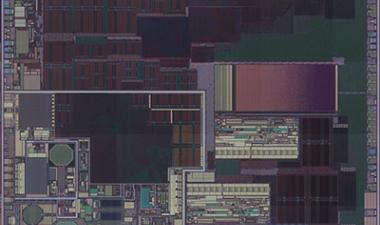

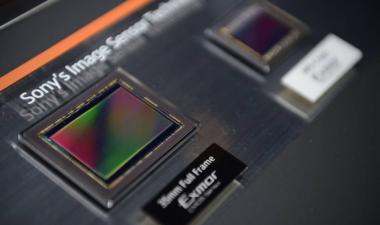

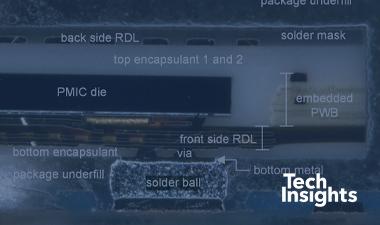

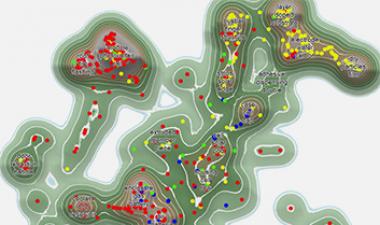

来自索尼和三星的最近0.8μm的像素如图3所示,以及DTI结构的概述。对于这些特定的芯片,索尼更喜欢150nm宽,氧化物填充的B-DTI结构,而三星更喜欢110nm宽,聚填充的F-DTI结构。

索尼的DTI解决方案在工艺流程的后期实施,有助于其平面像素晶体管战略的延续。三星的F-DTI结构强制实现垂直传输门(VTG),但解决方案会导致完全隔离的Si岛。我们在研讨会(R02论文)上了解到,OmniVision的0.8µm像素将采用B-DTI和VTG结构。

图3:DTI在0.8μm生成像素中

在这个博客系列的最后一篇文章中,我们将介绍非拜耳滤色器阵列的主题,以及三种类型的相位检测自动聚焦(PDAF)像素。

值得信赖的技术情报提供者

自2006年以来,TechInsights一直处于图像传感器竞争技术情报的最前沿,并始终率先报告关键技术要素。所有前10名的图像传感器设计公司都是我们的用户,所有前3名的图像传感器铸造厂都是我们的用户。